## AN INTRODUCTION TO THERMAL-ELECTRICAL COUPLING IN BIPOLAR TRANSISTORS

K. J. Negus<sup>1</sup>, M. M. Yovanovich<sup>2</sup>, and D. J. Roulston<sup>3</sup>

Microelectronics Heat Transfer Laboratory

University of Waterloo

Waterloo, Ontario, Canada

#### ABSTRACT

An approximate model to illustrate thermal-electrical coupling in bipolar transistors has been developed with a thermal model that accounts for two-dimensional, non-linear heat conduction in a particular transistor structure. The effect of thermal-electrical coupling on the terminal characteristics of the device is shown to be substantial and the phenomenon of thermal instability or thermal runaway is also demonstrated using this thermal-electrical model. A parametric study of a hypothetical transistor shows that major improvements in the operating range of a bipolar transistor can be realized through decreased thermal resistance.

### NOMENCLATURE

- half-width of emitter stripe

A - total emitter area

- half center-to-center spacing of adjacent emitter stripes

D<sub>n</sub> - diffusion constant for electrons

electronic charge

E, - bandgap

- transconductance

- base Gummel number

H(·) - Heaviside Unit Step Function

Is - base current

Ic - collector current

$I_{C \max}$  - maximum allowable collector current for a given  $V_{CE}$

- collector current at onset of thermal instability

- maximum allowable collector current for any  $V_{CE}$

- thermal conductivity

L. - effective emitter length

- intrinsic carrier concentration

No - constant used in modelling ni

power law coefficient for thermal conductivity model

- heat flux

total power dissipation

- linearized thermal resistance of the transistor

Graduate Research Assistant Professor, Member ASME

Professor, Department of Electrical Engineering

- thermal resistance exterior to the silicon die

REE - finite emitter electrical resistance

- thickness of die

T - temperature

$R_{\infty}$

$T_b$

- temperature at base of die

$ar{T_c}$  - average or representative emitter contact temperature

$T_{\infty}$  - ambient temperature

U - transformed temperature

$V_{BE}$  - forward bias of base to emitter

V<sub>CE</sub> - reverse bias of collector to emitter

$V_{br}$  - breakdown voltage of transistor

x, z - Cartesian coordinate system

#### Greek Symbols

$\alpha$  - aspect ratio of unit cell ( $\equiv t/b$ )

$\epsilon$  - relative emitter width ( $\equiv a/b$ )

λ - Boltzmann's constant

$\mu_n$  - electron mobility

#### Subscripts

B - refers to base of transistor

C - refers to collector of transistor

E - refers to emitter of transistor

n - refers to series solution

~ refers to ambient conditions

### INTRODUCTION

In recent years the cooling of integrated circuit chips in electronic equipment has received considerable attention. The reasons usually cited for this concern about excessively high temperatures in semiconductor devices are ones of degradation of reliability due to both performance variations and component failures. These concerns are quite legitimate. For example, with field-effect devices high temperature operation results in large threshold voltage changes, lower channel mobility (or slower "speed"), and an exponential increase in leakage currents. In logic applications any one or all of these effects can lead to substantial increases in error rates. Furthermore, with bipolar devices there exists a problem where thermal instability can lead potentially to physical destruction of the transistor. Yet another

concern is that of fatigue failures of metal interconnects due to high temperature cycling. However, even in the absence of these "excessive" or "damaging" temperatures, an incentive to compute device temperatures still exists simply to accurately predict the electrical performance of semiconductor devices in real circuits. This is especially true for bipolar transistors where in many cases the coupling between the thermal and electrical device performance can be quite strong. The goal of this work is to demonstrate how parameters which appear to affect only the thermal characterization of a bipolar transistor can also influence considerably the electrical performance of the device. This goal is achieved by developing a realistic approximate model for heat conduction in a high-power transistor structure and then coupling this model with an extremely simplified electrical model for the bipolar transistor.

## THEORETICAL DERIVATION

Thermal Model

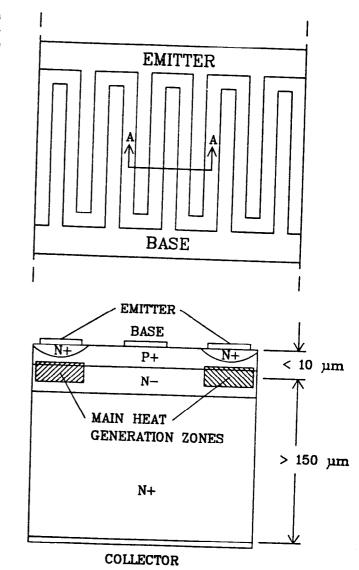

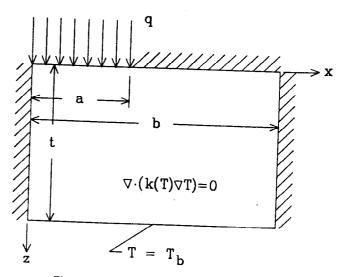

An idealized view of a large-scale bipolar transistor which might be used for high-power switching applications is shown in Fig. 1. This transistor consists of multiple emitter "fingers" which act electrically in parallel. For many typical transistors where the thickness of the silicon die is on the order of 200  $\mu m$ , most of the voltage drop in the device occurs directly underneath the emitter contacts within several  $\mu m$  from the surface. Thus the non-uniform heat generation within the device is often approximated by a uniform heat flux applied to the emitter contact as in the previous work of Latif (1979) and Katsueda, et al. (1984). The actual magnitude of this heat flux, however, will be shown in the next section to be a complex function of the transistor biasing conditions and the emitter contact temperature. The geometric symmetry of the transistor structure shown in Fig. 1 can also be utilized to simplify the model for heat conduction in the silicon die. By further assuming that the heat conduction is predominantly two-dimensional since the emitter stripe lengths are often much larger than the die thickness, an approximate model which characterizes heat conduction in the transistor is derived as shown in Fig. 2.

Heat conduction in the silicon die as modeled in Fig. 2 is governed by the partial differential equation

$$\nabla \cdot (k(T)\nabla T) = 0 \tag{1}$$

subject to the boundary conditions

$$k(T(x,0))\frac{\partial T}{\partial z}(x,0) = qH(a-x) \qquad 0 \le x \le b \qquad (2)$$

$$T(x,t) = T_b \qquad 0 \le x \le b \qquad (3)$$

$$\frac{\partial T}{\partial x}(0,z) = 0 \qquad 0 \le z \le t \qquad (4)$$

$$\frac{\partial T}{\partial x}(b,z) = 0 \qquad 0 \le z \le t \qquad (5)$$

where  $H(\cdot)$  is the Heaviside Unit Step Function and  $T_b$  the temperature at the base of the die.

Note that the temperature-dependent thermal conductivity of the silicon die creates a non-linear problem. Fortunately, Ozisik (1980) has shown that an entirely linear problem can be used to characterize Eqs. (1) to (5) by introducing the integral transformation

$$U = \int_{T_{ref}}^{T} \frac{k(T')}{k(T_{ref})} dT'$$

(6)

For both silicon and gallium arsenide, excellent correlations of available data for thermal conductivity versus temperature (Maycock, 1967) can be made using the form

Fig. 1 Typical bipolar transistor structure for high-power switching applications

Fig. 2 Idealized thermal model for transistor

$$k(T) = k_{\infty} \left(\frac{T}{T_{\infty}}\right)^{p} \tag{7}$$

where  $k_{\infty}$  is the thermal conductivity at the ambient temperature  $T_{\infty}$  (usually 300 K) and p is determined to best fit the experimental data. With k(T) given by Eq. (7) and  $T_{ref}$  set to  $T_{\infty}$ , transformed temperature in the silicon die is then

$$U = \frac{T_{\infty}}{p+1} \left[ \left( \frac{T}{T_{\infty}} \right)^{p+1} - 1 \right] \qquad (p \neq -1)$$

(8)

or conversely

$$T = T_{\infty} \left[ 1 + (p+1) \frac{U}{T_{\infty}} \right]^{\frac{1}{p+1}}$$

(9)

In terms of the transformed temperature Eqs. (1) to (5) become

$$\nabla^2 U = 0 \tag{10}$$

$$k_{\infty} \frac{\partial U}{\partial x}(x,0) = qH(a-x)$$

$0 \le x \le b$  (11)

$$U(x,t) = \frac{T_{\infty}}{p+1} \left[ \left( \frac{T_b}{T_{\infty}} \right)^{p+1} - 1 \right] \qquad 0 \le x \le b \quad (12)$$

$$\frac{\partial U}{\partial x}(0,z) = 0 \qquad 0 \le z \le t \quad (13)$$

$$\frac{\partial U}{\partial x}(b,z) = 0 \qquad 0 \le z \le t \quad (14)$$

A solution to this linear problem can be derived analytically using the method of separation of variables. Consideration of Eqs. (10), (13) and (14) leads to the series solution (Negus and Yovanovich, 1986)

$$U = C + Dz + \sum_{n=1}^{\infty} \left[ A_n \cosh \frac{n\pi z}{b} + B_n \sinh \frac{n\pi z}{b} \right] \cos \frac{n\pi x}{b}$$

(15)

Application of the boundary condition at the base of the die (Eq. (12)) yields

$$D = -\frac{q\epsilon}{k}... \tag{16}$$

$$C = \frac{qa}{k_{\infty}}\alpha + \frac{T_{\infty}}{p+1} \left[ \left( \frac{T_b}{T_{\infty}} \right)^{p+1} - 1 \right]$$

(17)

$$B_n = -A_n \coth n\pi\alpha \tag{18}$$

The aspect ratio  $\alpha$  and the relative emitter width  $\epsilon$  are defined

$$\alpha \equiv t/b \tag{19}$$

$$\epsilon \equiv a/b$$

(20)

where t is the thickness of the silicon die, a the half-width of the emitter stripe, and b half the center-to-center spacing of adjacent emitter stripes.

The remaining unknowns, the  $A_n$ , are determined by applying the **crthogonality** property of the eigenfunctions  $\cos(n\pi x/b)$  to Eq.(11) to give

$$A_n = \frac{2qb\sin n\pi\epsilon}{k_{\infty}n^2\pi^2\coth n\pi\alpha}$$

(21)

A thermal resistance for the transistor is now defined as

$$R_t = \frac{\bar{U}_c - U(z=t)}{Q} \tag{22}$$

where the average transformed contact temperature is

$$\bar{U}_{z} = \frac{1}{a} \int_{0}^{a} U(x,0) dx \tag{23}$$

and the total power dissipation of the transistor is related to the uniform heat flux q according to

$$Q = 2L_{eff}aq (24)$$

where  $L_{eff}$  is the effective total emitter stripe length. An analytical expression for  $R_t$  can then be derived as

$$R_{t} = \frac{1}{2k_{\infty}L_{eff}} \left\{ \alpha + \frac{2}{\pi^{3}\epsilon^{2}} \sum_{n=1}^{\infty} \frac{\sin^{2} n\pi\epsilon}{n^{3}} \tanh n\pi\alpha \right\}$$

(25)

From Eq. (9) an average or "representative" emitter contact temperature is

$$\bar{T}_{c} = T_{\infty} \left[ 1 + (p+1) \frac{\bar{U}_{c}}{T_{\infty}} \right]^{\frac{1}{p+1}}$$

$$= T_{\infty} \left[ \frac{p+1}{T_{\infty}} Q R_{t} + \left( \frac{T_{b}}{T_{\infty}} \right)^{p+1} \right]^{\frac{1}{p+1}}$$

(26)

The base temperature at the bottom of the silicon die is related to the ambient temperature by the simple relationship

$$T_b = T_{\infty} + QR_{\infty} \tag{27}$$

where  $R_{\infty}$  is the external thermal resistance from the die to ambient. The average emitter temperature of the bipolar transistor described in this work is then expressed in terms of the power dissipation Q and the resistances  $R_t$  and  $R_{\infty}$  according to

$$\bar{T}_{c} = T_{\infty} \left[ \frac{p+1}{T_{\infty}} Q R_{t} + \left( 1 + \frac{Q R_{\infty}}{T_{\infty}} \right)^{p+1} \right]^{\frac{1}{p+1}}$$

(28)

#### Electrical Model

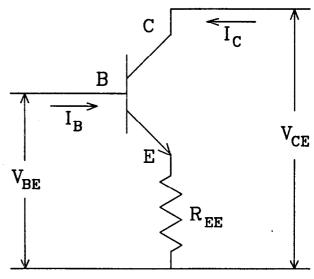

In the previous section a relationship between the average emitter temperature and the power dissipation of the transistor has been derived. In this section a simplified electrical model of the transistor is presented to provide a second relationship between power dissipation and average emitter temperature. A schematic diagram of a bipolar transistors as a three-terminal device is shown for the common-emitter configuration in Fig. 3. In most applications where the

Fig. 3 Schematic representation of transistor for common-emitter configuration

bipolar transistor is useful, the collector current  $I_C$  is much greater than the base current  $I_B$  and the collector-emitter bias  $V_{CE}$  is much greater than the base-emitter bias  $V_{BE}$ . For this case of  $I_C \gg I_B$  and  $V_{CE} \gg V_{BE}$  the power dissipation of the transistor is approximately

$$Q = I_C V_{CE} \tag{29}$$

The goal of a bipolar transistor model is usually to accurately relate  $I_C$  to  $V_{CE}$  and  $V_{BE}$ . One model which provides realistic predictions for many transistors is the Gummel-Poon model as described by Getreu (1978). With some further assumptions this model can be simplified to

$$I_C = \frac{eAn_i^2 D_n}{G_b} \exp\left[\frac{e}{\lambda T} (V_{BE} - I_C R_{EE})\right]$$

(30)

for the transistor illustrated schematically in Fig. 3. In this model e is the electronic charge ( $e=1.60\times 10^{-19}$  Coulombs) and  $\lambda$  is Boltzmann's constant ( $\lambda=8.62\times 10^{-5}$  eV/K). The effective emitter area is A and the base Gummel number is  $G_b$ . In this work  $G_b$  is treated as a process constant for a given transistor although in reality it is a non-linear function of  $V_{BE}$  and  $V_{CE}$ . This model also assumes that the transistor is maintained at some uniform temperature T which is obviously not entirely justified. However, the region which most affects the collector current  $I_C$  is the emitter-base junction. Since the emitter-base junction is typically within a few  $\mu$ m from the top surface of the die, this region can be approximated as uniform in temperature with a value given by the average emitter temperature  $\bar{T}_c$  (often referred to as the "junction" temperature). The diffusion constant for electrons  $D_n$  is related to the electron mobility  $\mu_n$  for moderate base doping levels by the Einstein relationship (Sze, 1981).

$$D_n = \frac{\lambda T}{e} \mu_n \tag{31}$$

where the mobility versus temperature relationship can often be modeled as (Sze, 1981)

$$\mu_n = \mu_{n\infty} \left(\frac{T}{T_{\infty}}\right)^{-3/2} \tag{32}$$

The intrinsic carrier concentration n; can be shown to be (Sze, 1981)

$$n_i^2 = N^* T^3 \exp\left[-\frac{E_g}{\lambda T}\right] \tag{33}$$

where for silicon  $N^*\approx 1.08 \times 10^{31} {\rm cm^{-6} K^{-3}}$  and  $Eg\approx 1.1$  eV for 300 < T < 500 K.

Upon replacing T by  $\bar{T}_c$  and substituting Eqs. (31) – (33) into Eq. (30), the electrical model for  $I_C$  becomes

$$I_C = \frac{\lambda \mu_{n\infty} A N^* T_{\infty}^{3/2}}{G_b} \bar{T}_c^{5/2} \exp\left[\frac{e(V_{BE} - I_C R_{EE}) - E_g}{\lambda \bar{T}_c}\right]$$

(34)

If  $I_C$  and  $V_{CE}$  are specified for a given transistor, the average emitter temperature can be computed directly from Eqs. (28) and (29). Inversion of Eq. (34) then gives the base-emitter bias as

$$V_{BE} = I_{C}R_{EE} + \frac{E_{g}}{e} + \frac{\lambda \bar{T}_{e}}{e} \ln \left[ \frac{I_{C}G_{b}}{\lambda \mu_{n\infty} A N^{*} T_{\infty}^{3/2} \bar{T}_{e}^{5/2}} \right]$$

(35)

## TERMINAL CHARACTERISTICS

The importance of thermal analysis to the accurate prediction of bipolar transistor performance can be illustrated by examining the terminal characteristics of a device both with and without consideration of thermal-electrical coupling. The bipolar transistor to be studied has all of its parameters pertinent to the preceding analysis listed in Table 1. This transistor, although hypothetical, is loosely based on a device studied by Latif (1979) and is indicative of a high-power switching device attached to a copper heat sink. Note that the device also has a maximum collector current limit,  $I_{\rm max}$ , and a maximum collector-emitter voltage,  $V_{br}$ . These limits arise from physical phenomena which are not accounted for in the extremely simplified electrical model of this work.

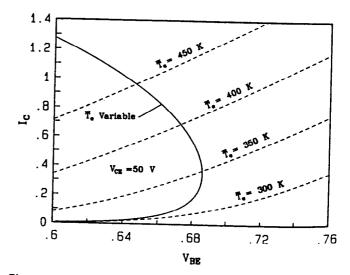

Typical terminal characteristics for this device are illustrated in Fig. 4 for the default parameter values in Table 1. The solid curve of Fig. 4 reflects the  $I_C$  versus  $V_{BE}$  behaviour for fixed  $V_{CE}$  as predicted by the thermal-electrical model derived in this work. The dashed curves are predictions of  $I_C$  versus  $V_{BE}$  for fixed device temperatures where thermal-electrical coupling is ignored. An inspection of Fig. 4 shows that substantial errors in the prediction of  $I_C$  for a given  $V_{BE}$  and  $V_{CE}$  can result when fixed device temperatures are assumed. Furthermore even larger errors occur in the prediction of the transconductance of the device. Transconductance is an important parameter in predicting small-signal device response and is defined as

| Parameter                                                                                                                    | Default Value                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $a$ $b$ $t$ $L_{eff}$ $T_{\infty}$ $k_{\infty}$ $p$ $R_{\infty}$ $G_b$ $\mu_{n\infty}$ $R_{ee}$ $I_{max}$ $V_{br}$ $T_{max}$ | 20 μm<br>60 μm<br>200 μm<br>1 cm<br>300 K<br>1.31 W/cm·K<br>-1.33<br>1 K/W<br>10 <sup>13</sup> cm <sup>-2</sup><br>300 cm <sup>2</sup> /V·s<br>.14 Ω<br>12 A<br>200 V<br>500 K |

Table 1. Default values of physical parameters for the transistor under study

Fig. 4 Terminal characteristics for default transistor at  $V_{CE}=50\,$  V

$$g_m = \left. \frac{\partial I_C}{\partial V_{BE}} \right|_{V_{CE}} \tag{36}$$

or essentially the slope of the  $I_C$  versus  $V_{BE}$  curve. With the simple electrical model assumed in this work,  $g_m$  is always found to be positive and finite when thermal-electrical coupling is ignored. However, Fig. 4 shows that in reality the transconductance can become unbounded and even negative with increasing collector current  $I_C$  for fixed  $V_{CE}$ .

# THERMAL INSTABILITY AND SAFE OPERATING AREA

For most practical purposes bipolar transistors can not be operated in the negative-transconductance (or negative-differential resistance) region of Fig. 4. A major reason for this is the potentially destructive instability which can result when attempting to turn off the device. For example, consider the transistor described in Table 1 operating as shown in Fig. 4 at  $V_{BE}=.664~V,~I_{C}=.8~A,~ar{T}_{c}=420$ K, and  $V_{CE} = 50$  V. If one attempts to turn off the device by decreasing  $V_{BE}$  over a sufficient period of time then  $I_C$  will actually increase. As the collector current increases the emitter temperature also increases as indicated on Fig. 4 and eventually leads to actual physical destruction of the device if uncontrolled. An example of such a situation occurs with discrete power devices used to switch large inductive loads such as AC motors. In these applications switching occurs over several milliseconds or longer which thus leads to component failures as described in Latif (1979). This phenomenon is often referred to as thermal instability or thermal runaway and has been the catastrophic failure mechanism for countless bipolar transistors in many different applications over the past 30 years.

The actual operating point at which thermal instability can begin to occur is determined by examining the differential resistance of the transistor. As shown in Fig. 4 the transition to a negative-transconductance region occurs when this differential resistance is zero. From Eq. (35) the differential resistance can be derived as

$$\frac{\partial V_{BB}}{\partial I_{C}}\Big|_{V_{CB}} = R_{EE} + \frac{\lambda}{e} \left\{ \frac{\bar{T}_{c}}{I_{C}} + \frac{\partial \bar{T}_{c}}{\partial I_{C}} \Big|_{V_{CB}} \left[ \ln \left( \frac{I_{C}G_{b}}{\lambda \mu_{n\infty} A N^{*} T_{\infty}^{3/2} \bar{T}_{c}^{5/2}} \right) - \frac{5}{2} \right] \right\}$$

(37)

where Eqs. (28) and (29) can be combined to give

$$\mathbf{T}_{\sigma} = T_{\infty} \left[ \frac{p+1}{T_{\infty}} R_t V_{CE} I_C + \left( 1 + \frac{R_{\infty} V_{CE} I_C}{T_{\infty}} \right)^{p+1} \right]^{\frac{1}{p+1}}$$

(38)

and with some algebraic manipulation,

$$\left. \frac{\partial \bar{T}_c}{\partial I_C} \right|_{V_{CE}} = \left( \frac{T_{\infty}}{\bar{T}_c} \right)^p V_{CE} \left[ R_t + R_{\infty} \left( \frac{R_{\infty} V_{CE} I_C}{T_{\infty}} \right)^p \right]$$

(39)

The collector current above which the transistor will be thermally metable,  $I_{Cu}$ , is thus given for a particular  $V_{CE}$  by

$$\left. \frac{\partial V_{BE}}{\partial I_C} \right|_{V_{CB}} (I_C = I_{Cu}) = 0 \tag{40}$$

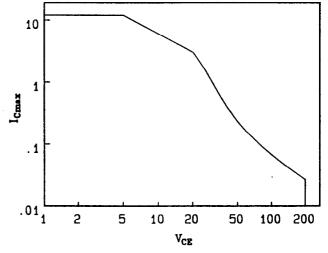

This current represents an upper bound on the allowable collector current for a given  $V_{CE}$ . In many cases though the transistor may be thermally limited at collector currents below  $I_{Cu}$  due simply to intolerable temperature rises within the die. The maximum temperature limitation may arise from factors such as limits on expectation of metal interconnects on the die or unacceptable variation of device behaviour over wide temperature ranges. Manufacturers usually supply a curve called the Safe Operating Area or SOA of the transitor which shows graphically the maximum allowable collector current for the entire range of  $V_{CE}$ . A typical SOA curve is shown in

Fig. 5 for the default transistor described in Table 1. The curve can be described in terms of three distinct regions. In region 1 the device is electrically limited to a maximum current  $I_{\rm max}$  for reasons which will not be discussed in this work. Region 2 is essentially bounded by a constant power dissipation curve ( $I_{C\,\rm max}V_{CE}=Q_{\rm max}$ ) corresponding to the maximum allowable temperature for the transistor (assumed to be 500 K in this case). Thermal instability as described by Eqs. (37) – (40) limits the collector current to  $I_{C\,\rm max}=I_{Cu}$  in region 3 which is also terminated by a maximum voltage limitation.

The next sections examine how variations in parameters which describe the transistor's physical system affect the device performance and SOA curve. Obviously a decrease in overall thermal resistance will increase the Safe Operating Area in region 2 by allowing a higher maximum power dissipation for a given maximum temperature. It is not obvious beforehand, however, what effect thermal resistance has on the thermal instability which limits the collector currents in region 3 of the SOA curve.

# EFFECT OF EMITTER SPACING AND DIE THICKNESS

Variation of the emitter spacing or die thickness of the transistor will obviously affect the internal thermal resistance of the transistor. General trends for the effect of transistor geometry on  $I_{C\,\mathrm{max}}$  can be investigated using the thermal-electrical model developed in this work. The results are presented in tabular form for  $V_{CE}=10~\mathrm{V}$  and  $V_{CE}=50~\mathrm{V}$ .

The effect of varying emitter spacing is presented in Table 2 by using values of b from 50 to 100  $\mu m$ . For  $V_{CE}=10$  V the current limitation arises from the requirement that  $\bar{T}_c$  not exceed 500 K. Increased emitter spacing decreases the internal thermal resistance and thus allows higher collector currents for a given maximum temperature. When  $V_{CE}=50$  V the current limitation is due to thermal instability occurring at temperatures far below  $T_{\rm max}=500$  K. Changes in emitter spacing are seen to have a more pronounced effect on  $I_{C\,\rm max}$  in this case. This can be explained by noting that decreased thermal resistance causes thermal instability to occur at higher temperatures as reported in Table 2. Thus  $I_{C\,\rm max}$  can be increased considerably in this region by increasing the emitter spacing. The major penalty to be paid for increasing emitter spacing is one of inefficient utilization of available silicon area.

In Table 3  $I_{C\,\mathrm{max}}$  is given as a function of the die thickness with all other physical parameters assumed to have their default values. The general trends observed are similar to those of Table 2. When

Fig. 5 Safe Operating Area for default transistor

|                                              | $V_{CE} = 10 \text{ V}$                                              |                                                             | $V_{CE} = 50 \text{ V}$                                      |                                                             |

|----------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|

| b<br>(μm)                                    | I <sub>C max</sub> (A)                                               | $ar{T_c(I_{C 	ext{ max}})} \ (	ext{K})$                     | I <sub>C max</sub> (A)                                       | $ar{T_c(I_{C	ext{max}})}$ (K)                               |

| 50<br>55<br>60<br>65<br>70<br>75<br>80<br>90 | 5.50<br>5.74<br>6.00<br>6.22<br>6.42<br>6.60<br>6.76<br>7.05<br>7.28 | 500<br>500<br>500<br>500<br>500<br>500<br>500<br>500<br>500 | .193<br>.212<br>.231<br>.248<br>.265<br>.282<br>.298<br>.327 | 327<br>328<br>330<br>331<br>332<br>334<br>335<br>337<br>339 |

Table 2. Variation of  $I_{C \max}$  and  $\bar{T}_c(I_{C \max})$  versus emitter spacing

|                                                             | $V_{CE} = 10 \text{ V}$                                              |                                                                     | $V_{CE} = 50 \text{ V}$                                      |                                                             |

|-------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|

| t<br>(µm)                                                   | I <sub>C max</sub> (A)                                               | $egin{aligned} ar{T_c}(I_{C 	ext{ max}}) \ (	ext{K}) \end{aligned}$ | I <sub>C max</sub> (A)                                       | $ar{T_c(I_{C	ext{max}})}$ $	ext{(K)}$                       |

| 150<br>175<br>200<br>225<br>250<br>300<br>350<br>400<br>500 | 7.00<br>6.46<br>6.00<br>5.61<br>5.26<br>4.69<br>4.23<br>3.86<br>3.28 | 500<br>500<br>500<br>500<br>500<br>500<br>500<br>500<br>500         | .323<br>.270<br>.231<br>.201<br>.179<br>.145<br>.122<br>.106 | 337<br>333<br>330<br>328<br>326<br>323<br>322<br>321<br>319 |

Table 3. Variation of  $I_{C \max}$  and  $\bar{T}_c(I_{C \max})$  versus die thickness

the die thickness is increased the thermal resistance increases and  $I_{C\,\mathrm{max}}$  is reduced. For the thermal instability region ( $V_{CE}=50~V$ ) the decrease in  $I_{C\,\mathrm{max}}$  can be substantial.

# EFFECT OF EXTERNAL THERMAL RESISTANCE

In Table 4  $I_{C \max}$  is reported for different values of the thermal resistance  $R_{\infty}$  from the base of the die to ambient. As expected  $I_{C \max}$  decreases as  $R_{\infty}$  increases. This indicates that the performance range for a given transistor can be greatly increased by providing a superior heat dissipation system.

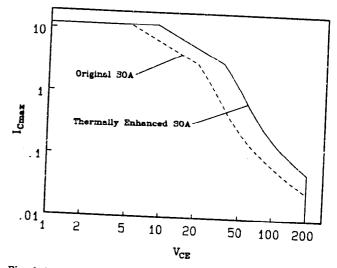

A transistor with increased emitter spacing, decreased die thickness and decreased external thermal resistance should have an increased Safe Operating Area. With the "best" parameter values from Tables 2-4 used to describe a thermally enhanced transistor (b=100  $\mu$  m, t=150  $\mu$  m,  $R_{\infty}=.5$  K/W), the increase in SOA from the default transistor is shown in Fig. 6.

|                                                            | $V_{CE}=10~ m{V}$                                            |                                                                             | $V_{CE} = 50 \text{ V}$                              |                                                                   |

|------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------|

| $R_{\infty}$ (K/W)                                         | I <sub>C max</sub> (A)                                       | $egin{aligned} 	ilde{T_c}(I_{C	ext{max}}) \ 	ilde{	ext{(K)}} \end{aligned}$ | I <sub>C max</sub> (A)                               | $egin{aligned} ar{T_c}(I_{C	ext{max}}) \ (	ext{K}) \end{aligned}$ |

| .50<br>.75<br>1.00<br>1.25<br>1.50<br>2.00<br>3.00<br>5.00 | 7.32<br>6.59<br>6.00<br>5.52<br>5.13<br>4.49<br>3.62<br>2.62 | 500<br>500<br>500<br>500<br>500<br>500<br>500<br>500                        | .380<br>.288<br>.231<br>.190<br>.162<br>.124<br>.084 | 340<br>334<br>330<br>327<br>325<br>322<br>319<br>317              |

Table 4. Variation of  $I_{C\,{

m max}}$  and  $ar{T}_c(I_{C\,{

m max}})$  versus external thermal resistance

Fig. 6 Increased Safe Operating Area for thermally enhanced transistor

## CONCLUSIONS

An approximate model has been developed to describe thermalelectrical coupling in bipolar transistors. The electrical model is extremely simplified but the thermal model consists of an analytical solution for two-dimensional heat conduction with non-linear thermal conductivity. The methodology could also be extended to more complex transistor models and to three-dimensional thermal models.

Thermal-electrical coupling has been found to have a major effect on the terminal characteristics of a bipolar transistor. This coupling also leads to thermal instability which can limit the tolerable current through the device. In some cases thermal instability can occur at device temperature rises of less than 20°C above ambient.

A parametric study for a hypothetical transistor has revealed that decreasing the thermal resistance of the system permits increases in device operating range which can be substantial. It is thus imperative that accurate thermal analysis and prediction be made available to maximize the utility of a bipolar transistor in a given system.

## ACKNOWLEDGEMENTS

The authors acknowledge the financial support of this work by the Natural Sciences and Engineering Research Council of Canada under operating grant A7455 for Dr. Yovanovich and from a Postgraduate Scholarship for Mr. Negus.

### REFERENCES

- Getreu, I.E., 1978, Modeling the Bipolar Transistor, Elsevier, New York.

- Katsueda, M., et al., 1984, "Large Scale Thermal Analysis of Power Integrated Devices", Trans. of the IECE of Japan, Vol. E67, No. 2.

- Latif, M., 1979, "A Numerical Study of Transistor Behaviour Including Thermal Effects", Ph.D. Thesis, Department of Electrical Engineering, University of Waterloo, Waterloo, Canada.

- Maycock, P.D., 1967, "Thermal Conductivity of Silicon, Germanium, III-V Compounds and III-V alloys", Solid-State Electronics, Vol. 10, pp. 161-168.

- Negus, K.J. and Yovanovich, M.M., 1986, "Thermal Analysis and Optimization of Convectively-Cooled Microelectronic Circuit Boards", Heat Transfer in Electronic Equipment 1986, ASME HTD-Vol. 57, New York, pp. 167-175.

- Ozisik, M.N., 1980, Heat Conduction, Wiley, New York.

- Sze, S.M., 1981, Physics of Semiconductor Devices, Wiley, New York.