# THERMAL ANALYSIS AND OPTIMIZATION OF CONVECTIVELY-COOLED MICROELECTRONIC CIRCUIT BOARDS

K. J. Negus, Graduate Research Assistant and M. M. Yovanovich, Professor Microelectronics Heat Transfer Laboratory Department of Mechanical Engineering University of Waterloo Waterloo, Ontario, Canada

### ABSTRACT

An approximate analytical solution to a fundamental basis problem for heat conduction in a convectively-cooled microelectronic circuit board has been derived by employing a novel approach for treating mixed boundary conditions. Results obtained with this solution indicate that increasing the chip spacing decreases the thermal resistance of the circuit board for many cooling configurations only if accompanied by an increased board thickness. Thus in many practical applications, little gain in thermal performance of the board is realized for chip center-to-center spacings greater than twice the chip width. In addition, the analytical solution has also been used to estimate the accuracy of the compound-fin model for one-dimensional steady heat conduction in a microelectronic circuit board.

### NOMENCLATURE

| a                                | - half-width of IC chip                                                                                  |

|----------------------------------|----------------------------------------------------------------------------------------------------------|

| A <sub>n</sub>                   | - series coefficient                                                                                     |

| Ъ                                | - half of the IC chip center-to-center                                                                   |

|                                  | spacing                                                                                                  |

| Bi <sub>1</sub> ,Bi <sub>2</sub> | - Biot numbers (Bi≡ht/k) for the top and                                                                 |

|                                  | bottom surfaces of the circuit board respectively                                                        |

| C<br>mn                          | <pre>- entries in coefficient matrix (Eqs. (25) or (A-l))</pre>                                          |

| E                                | - integral of errors squared in Eq. (17)                                                                 |

| g(ξ)                             | - function for non-homogeneous boundary condition (Eq. (19))                                             |

| G<br>n                           | - entries in right-hand side vector (Eqs. (26) or (A-5))                                                 |

| h <sub>1</sub> ,h <sub>2</sub>   | - convective heat transfer coefficients for<br>the top and bottom surfaces of the circuit                |

| h <sub>el</sub> ,h <sub>e2</sub> | board respectively - effective heat transfer coefficients for the top and bottom surfaces of the IC chip |

|                 | respectively                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------|

| k               | - homogeneous thermal conductivity                                                            |

| L               | <ul> <li>length of IC chip(s) into the circuit<br/>board</li> </ul>                           |

| m,n             | - series solution indices                                                                     |

| N               | - number of series coefficients                                                               |

| q               | - uniform heat flux                                                                           |

| $Q_1,Q_2$       | - total heat flow rates across top and                                                        |

| 1 2             | bottom surfaces of the IC chip respectively                                                   |

| R <sub>2</sub>  | - thermal resistance of heat flow path into the circuit board                                 |

| t               | - thickness of the circuit board                                                              |

| T               | - temperature                                                                                 |

| T <sub>c</sub>  | <ul> <li>average temperature rise on contact<br/>between IC chip and circuit board</li> </ul> |

| T <sub>oo</sub> | - free-stream cooling fluid temperature                                                       |

| x,y,z           | - Cartesian coordinate system                                                                 |

# Greek Symbols

| α            | - aspect ratio of the board (Et/b)                          |

|--------------|-------------------------------------------------------------|

| Y3,Y4        | - dimensionless constants defined by Eqs.                   |

| 3 4          | (14) and (A-4) respectively                                 |

| δ            | - Kronecker delta function (δ =0 for m≠n,                   |

| min          | $\delta$ =1 for m=n)                                        |

|              | mn Tor m-n)                                                 |

| Δ            | - function used to evaluate C_(Eq. (A-2))                   |

| mn           | mn                                                          |

| ε            | - relative contact size (Ξa/b)                              |

| η,ξ          | - dimensionless coordinate system (ξΞx/b,                   |

|              | η≣z/b)                                                      |

| Λ            | - function of Bi, and $\epsilon$ (Eq. (13))                 |

| n            | 4                                                           |

| τ<br>n       | - function used to evaluate C (Eq. (A-3))                   |

| φ_(ξ)        | - functions for non-homogeneous boundary                    |

| 'n           | condition (Eq. (18))                                        |

| ψ            | - dimensionless resistance of fundamental                   |

| Ψ            |                                                             |

|              | basis problem (≣k L R ) given by Eq. (31)                   |

| $^{\Psi}$ CF | <ul> <li>dimensionless resistance estimated from</li> </ul> |

|              | compound-fin model (Eqs. (35) or (40))                      |

| ψ*           | - dimensionless resistance estimated from                   |

| CF           |                                                             |

|              | modified compound-fin model (Eq. (43))                      |

#### Subscripts

- refers to the series solution - refers to the top and bottom surfaces 1,2 respectively

#### INTRODUCTION

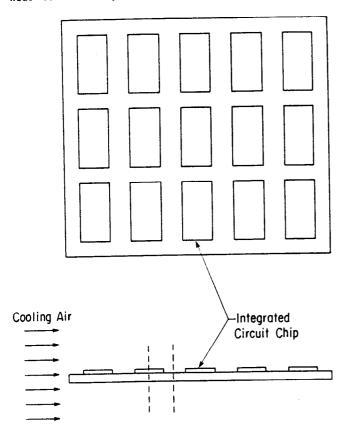

The present trend towards increasing power densities in modern integrated circuits requires a greater emphasis on thermal considerations in microelectronics packaging. If the simple and relatively economical air cooling scheme illustrated in Fig. 1 continues to be employed, it becomes imperative that the thermal resistance of this configuration be minimized. This goal can be achieved both by maximizing the convective heat transfer rates and by optimizing the circuit board layout for a given air cooling sit-

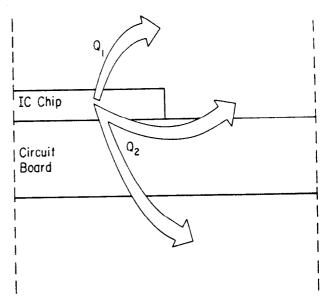

As shown in Fig. 2, the heat generated within a typical integrated circuit chip on a printed circuit board is removed through two main heat flow paths. The thermal resistance of the heat flow path  $Q_{\mbox{\scriptsize l}}$ through the top of the chip can be minimized both by lowering the thermal resistance between the semiconductor devices and the top surface of the chip and by maximizing the effective heat transfer rates from the top surface of the chip. This latter goal might be achieved by the use of either extended surfaces (i.e. external fins) or enhanced convective cooling (i.e. turbulence generators). The thermal resistance of the second major heat flow path Q, shown in Fig. 2 can be minimized by lowering the thermal resistance between the semiconductor devices and the bottom casing of the chip, by providing a good contact or heat conduction path between the bottom casing and

Fig. 1 Air Cooling of Integrated Circuit Chips on a Microelectronic Circuit Board

Main Heat Flow Paths from an Integrated Circuit Chip

circuit board, and by optimizing the circuit board configuration for a given air cooling arrangement.

These two main heat flow paths are, in reality, coupled both by the interaction with the thermalfluid boundary layer above the circuit board and by heat conduction within the integrated circuit chip. If, however, the physical approximation of modelling the two heat flow paths Q and Q as thermal resistances acting in parallel is made, then with the methods developed in this paper it can be shown that as much as 50% or even more of the total heat generation will flow through the bottom heat flow path Q for typical circuit board layouts and little contact resistance (for example, surface-mount packaging). Therefore a tremendous motivation exists to optimize the circuit board configuration in an effort to reduce the overall thermal resistance of the cooling system and hence allow higher power densities for a given maximum device operating temperature. development of an approximate analytical tool which can permit such an optimization for a given cooling scheme is then the first major goal of this work.

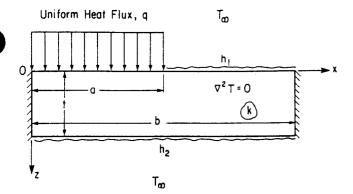

Accurate analysis of heat transfer due to aircooling of a microelectronic circuit board is a com-In this paper only a fundamental basis plex task. problem for heat conduction in the circuit board is examined. This basis problem then allows relative comparisons of the thermal resistances for different circuit board layouts so that a designer can quickly select a configuration which best compromises the goals of minimal cost and minimal thermal resist-The fundamental basis problem used to model circuit board heat conduction in this paper is shown in Fig. 3 where a uniform heat flux q enters a twodimensional rectangular region with adiabatic ends and uniform heat transfer coefficients h, and h on the top and bottom surfaces respectively. convenience the free-stream temperature of the cooling air is taken as  $T_{\infty} = 0$ . The assumption of uniform heat transfer coefficients reflects both the fact that in most cases h and h can only be esti-mated roughly beforehand and that this selection simplifies the analysis. By assuming that a "large" number of similar integrated circuit chips are evenly distributed over the circuit board the conservative

Fig. 3 Basis Problem for the Study of Thermal Resistance in a Microelectronic Circuit Board

(in terms of maximum temperature) assumption of adiabatic ends is chosen. Finally, prescribing a uniform heat flux into the circuit board allows objective comparisons of thermal resistance to be made only in terms of the parameters over which the designer has some direct control. Recent papers by Yovanovich (1976) and Negus and Yovanovich (1985) have also shown the relative insensitivity of thermal resistance to the exact form of the flux-specified boundary condition for complex heat conduction systems and that a uniform heat flux should give an upper bound on the true resistance of the board.

A more thorough analysis of heat transfer from integrated circuit chips on a printed circuit board requires a consideration of the coupling between the heat conduction in the circuit board and the behaviour of the thermal-fluid boundary layers surrounding the board (also known as the conjugate problem). In theory this entails a simultaneous solution of the momentum and energy equations in the cooling fluid and Laplace's equation in the board with potentially significant computational costs using standard numerical methods. However, a good approximate solution can be developed by combining integral boundary layer analysis with a one-dimensional or compound-fin model of heat conduction in the board as proposed by Culham (1985). Thus a second major goal of this paper is to examine the limits of the one-dimensional or compound-fin model for heat conduction under typical air-cooling conditions.

## THEORETICAL DERIVATION

Under the assumptions of homogeneous, isotropic thermal conductivity k and steady-state conditions, heat conduction in the basis problem shown in Fig. 3 is governed by the following partial differential equation and boundary conditions:

$$\frac{\partial^2 \mathbf{r}}{\partial \mathbf{x}^2} + \frac{\partial^2 \mathbf{r}}{\partial \mathbf{z}^2} = 0 \tag{1}$$

$$\frac{\partial T}{\partial x}(0,z) = 0 \tag{2}$$

$$\frac{\partial T}{\partial x} (b,z) = 0 \tag{3}$$

$$k \frac{\partial T}{\partial z}(x,t) + h_2 T(x,t) = 0$$

(4)

$$-k \frac{\partial T}{\partial z}(x,0) + h(x)T(x,0) = q(x)$$

(5)

where

re

$$h(x) = \begin{cases} 0, & 0 \le x \le a \\ h_1, & a \le x \le b \end{cases}$$

(6)

$$q(x) = \begin{cases} q, & 0 \le x \le a \\ 0, & a \le x \le b \end{cases}$$

(7)

The solution to this problem governed by Laplace's equation with consideration of the three homogeneous boundary conditions of Eqs. (2), (3) and (4) is determined in a straightforward manner using the separation of variables technique to yield

$$T(\mathbf{x}, \mathbf{z}) = \frac{\mathrm{qt}}{\mathrm{k}} \left\{ D\left[1 - \frac{\mathrm{Bi}_{2} \eta}{\alpha (\mathrm{Bi}_{2} + 1)}\right] + \sum_{n=1}^{\infty} A_{n} \cos n \pi \xi \left[ \cosh n \pi \eta - \Omega_{n} \sinh n \pi \eta \right] \right\}$$

(8)

where  $\xi\equiv x/b$  and  $\eta\equiv z/b$  represent dimensionless coordinates, the factor qt/k which has dimensions of temperature permits dimensionless constants D and A , and the Biot number on the bottom surface and aspect ratio of the board are defined respectively as

$$Bi_{2} \equiv h_{2}t/k \tag{9}$$

$$\alpha \equiv t/b$$

(10)

In addition,

$$\Omega_{n} = \frac{\alpha n \pi \tanh n \pi \alpha + Bi_{2}}{\alpha n \pi + Bi_{2} \tanh n \pi \alpha}$$

(11)

Unfortunately though, the classical method of separation of variables can not account for the mixed boundary condition of Eq. (5) which arises when h(x) of Eq. (6) varies on z=0 for  $0 \le x \le b$ . To overcome this restriction a special approximate analytical technique must be developed to determine the unknown series coefficients  $A_n$  in Eq. (8) from the non-homogeneous boundary condition of Eq. (5). This procedure is initiated by relating the constant D in Eq. (8) to the series coefficients by substituting Eq. (8) into Eq. (5) and simply integrating from x=0 to x=b to give

$$D = \left[\varepsilon - \sum_{n=1}^{\infty} A_n \Lambda_n\right] / \gamma_3$$

(12)

where  $\Lambda_n = -Bi_1 \frac{\sin n\pi \epsilon}{n\pi}$  (13)

$$\gamma_3 = Bi_2/(Bi_2+1) + Bi_1(1-\epsilon)$$

(14)

and the Biot number for the top surface and the relative contact size of the chip on the circuit board are defined respectively as

$$Bi_{1} \equiv h_{1}t/k \tag{15}$$

$$\varepsilon \equiv a/b$$

(16)

The unknown series coefficients A must now be determined by substituting Eqs. (12) and (8) into Eq. (5) and rearranging terms such that the non-homogeneous boundary condition is expressed by the relationship

$$\sum_{n=1}^{\infty} A_n \phi_n(\xi) = g(\xi) \qquad 0 \le \xi \le 1$$

(17)

where the functions  $\phi_n(\xi)$  and  $g(\xi)$  are

$$\phi_{n}(\xi) = \cos n\pi \xi \left[ n\pi \Omega_{n} \alpha \gamma_{3} + Bi(\xi) \gamma_{3} \right] - \Lambda_{n} \left[ \frac{Bi_{2}}{Bi_{2} + 1} + Bi(\xi) \right]$$

(18)

$$g(\xi) = \gamma_3 \beta(\xi) - \varepsilon Bi(\xi) - \varepsilon Bi_2/(Bi_2+1)$$

(19)

where

$$Bi(\xi) = \begin{cases} 0 & , & 0 \leq \xi \leq \varepsilon \\ & & \end{cases}$$

$$Bi_{1} & , & \varepsilon \leq \xi \leq 1$$

$$(20)$$

$$\beta(\xi) = \begin{cases} 1 & , & 0 \leq \xi \leq \varepsilon \\ 0 & , & \varepsilon \leq \xi \leq 1 \end{cases}$$

(21)

In a classical separation of variables problem, the unknown series coefficients A would now be detmined by invoking an orthogonality property of eigenfunctions  $\phi$  ( $\xi$ ) over the interval of the non-homogeneous boundary condition (Fourier's Method). However in this case the functions  $\phi$  ( $\xi$ ) of Eq. (18) are not orthogonal over the range  $0 \le \xi \le 1$  because of the mixed boundary condition imposed on the top surface. Thus Fourier's Method cannot be applied to this problem and it would appear that a solution technique other than separation of variables should be utilized.

This is particularly frustrating because the solution obtained thus far satisfies both the governing partial differential equation and all of the homeneneous boundary conditions. A recent paper by Negus and Yovanovich (1984) has shown, at least for image methods applied to heat conduction, that excellent approximate solutions can be obtained by satisfying one or more boundary conditions only in a least-squares sense. This suggests that a finite number, N, of unknown series coefficients A might be determined by minimizing the continuous integral of errors squared in Eq. (17) defined as

$$E = \int_{0}^{1} [g(\xi) - \sum_{n=1}^{N} A_{n} \phi_{n}(\xi)]^{2} d\xi$$

(22)

Minimization of E is effected by requiring that

$$\frac{\partial E}{\partial A_m} = 0 \qquad m=1,2,3,\ldots, N \qquad (23)$$

which then creates the system of linear algebraic equations

$$\begin{bmatrix} c_{mn} \end{bmatrix} \begin{bmatrix} A_n \end{bmatrix} = \begin{bmatrix} G_n \end{bmatrix} \tag{24}$$

from which the unknown series coefficients A can be determined. The entries in the coefficient matrix

$[C_{mn}]$  and right-hand side vector  $\{G_n\}$  are defined as

$$C_{mn} = \int_{0}^{1} \phi_{n}(\xi) \phi_{m}(\xi) d\xi$$

(25)

$$G_{n} = \int_{0}^{1} g(\xi) \phi_{n}(\xi) d\xi$$

(26)

and exact expressions for  ${\tt C}_{\mbox{\footnotesize mn}}$  and  ${\tt G}_{\mbox{\footnotesize are contained in}}$  Appendix I.

An approximate solution for the temperature throughout the circuit board section of Fig. 3 is now available by combining Eq. (8) with the coefficients A found by solving the linear system of Eq. (24). In Furthermore, Negus (1985) has recently proven mathematically that as  $E \neq 0$  (or the number of coefficients, N, becomes arbitrarily large) the approximate solution obtained uniformly approaches the exact solution everywhere in the solution domain. Thus any desired degree of accuracy for this approximate solution can be achieved, at least in theory, by increasing the number of series coefficients in the solution.

It is interesting to note that in the limiting case where the functions  $\varphi_{\Pi}(\xi)$  are orthogonal on the range  $0 \leq \xi \leq 1$  (i.e. no mixed boundary condition), the off-diagonal entries in [C ] are zero and the series coefficients determined by this formulation are thus identical to those found by direct application of Fourier's Method. In practise it even appears that some "residual orthogonality" remains for the actual  $\varphi$  ( $\xi$ ) functions in this problem as inspections of the matrices [C  $_{mn}$ ] produced by Eq. (25)

clearly indicate significant diagonal dominance. Furthermore, it is also interesting to observe that the system of linear equations produced by this method of minimizing the integral of errors squared is identical to that which would result from direct application of Galerkin's Method in approximating the boundary condition of Eq. (17).

The thermal resistance,  $R_2$ , of the basis problem illustrated in Fig. 3 is given by the definition

$$R_2 = \frac{\bar{T}_c - T_\infty}{Q_0} \tag{27}$$

where in this problem  $T_{\infty}=0$  and  $Q_2$  is the total heat flow rate crossing the contact portion of the circuit board, or

$$Q_2 = q L a \tag{28}$$

where L is the length of the chip into the plane of the paper in Fig. 3. The average temperature rise on the contact portion of the circuit board is defined

$$\bar{T}_{c} = \frac{1}{a} \int_{0}^{a} T(x,0) dx \qquad (29)$$

Finally, a dimensionless thermal resistance parameter is introduced as

$$\psi \equiv \mathbf{k} \, \mathbf{L} \, \mathbf{R}_2 \tag{30}$$

The combination of Eqs. (8), (27), (28), (29)

and (30) then leads to the following approximate expression for  $\psi$  with N coefficients A determined by solving Eq. (24)

$$\psi \approx \frac{\alpha}{\varepsilon} \left\{ \left[ \varepsilon - \sum_{n=1}^{N} A_n \Lambda_n \right] / \gamma_3 + \frac{1}{\varepsilon} \sum_{n=1}^{N} \frac{A \sin n\pi\varepsilon}{n\pi} \right\}$$

(31)

OPTIMIZATION FOR SPECIFIC COOLING ARRANGEMENTS

The computation of the dimensionless thermal resistance as given by Eq. (31) requires the solution of Eq. (24) for some finite number of series coefficients A . Formulation of the system of equations is accomplished using the expressions given in Appendix I. These exact expressions for the matrix coefficients  $C_{\mbox{mn}}$  and  $G_{\mbox{might}}$  appear somewhat formidable but are actually quite simple to implement in BASIC on a personal computer. An extremely efficient decomposition process is used to solve the resultant system of equations which are diagonal dominant. The symmetric property of [C ] is also exploited to reduce both storage requirements and execution time. Up to 110 coefficients can be found by direct solution with compiled Microsoft BASIC on an IBM-PC with this limitation arising only from the 64 Kbyte maximum array space of this compiler.

Practical problems with convectively-cooled microelectronic circuit boards usually require anywhere from 10 to 200 coefficients to obtain accuracy better than 1% for  $\psi$  and typical execution times are under one minute. A somewhat larger number of coefficients are required to accurately compute the temperatures on the top surface although substantially fewer are needed to compute temperatures elsewhere. As might be expected from physical intuition, the case requiring the greatest number of coefficients occurs when the aspect ratio a is very small (a relatively thin board), the bottom surface is insulated  $(h_2 = 0)$ , and the top surface has a high convective heat transfer coefficient h1. When greater than 110 coefficients are required, the solution is still obtained using the IBM-PC but the coefficients are determined by block iteration. The system of equations given by Eq. (24) is ideally suited for block iterative techniques because of the diagonal dominance of  $\begin{bmatrix} \mathbf{C}_{\mathbf{m}\mathbf{n}} \end{bmatrix}$  and because the A decrease in value as n increases (usually only l iteration is required).

The dimensionless thermal resistance parameter  $\psi$  derived in the previous section is a function of four dimensionless parameters or

$$\psi = \psi (\alpha, \epsilon, Bi_1, Bi_2)$$

(32)

The aspect ratio  $\alpha$  and the relative contact size  $\epsilon$  describe the geometry of the board while the Biot numbers  $\mathrm{Bi}_1$  and  $\mathrm{Bi}_2$  reflect a combination of the convective-cooling arrangement, the thermal conductivity of the board, and the geometry. The use of these dimensionless groups reduces the number of unknowns in the basis problem of Fig. 3 from six (a, b, t, k, h<sub>1</sub>, h<sub>2</sub>) to four. Nonetheless, these four independent parameters can vary over wide ranges of values which makes it simply unfeasible to present extensive results in a paper of finite length.

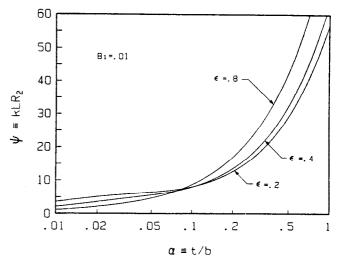

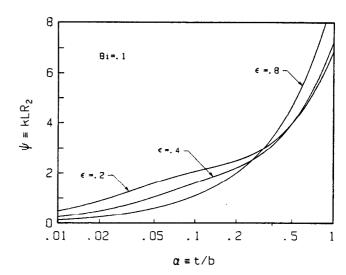

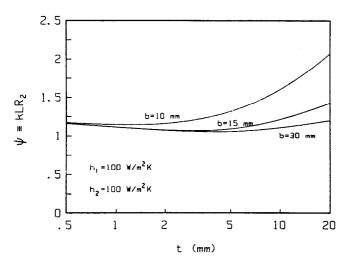

Presentation of graphical results is greatly simplified by considering only the often-encountered case for forced-air cooling where top and bottom heat transfer coefficients are approximately identical, or Bi  $_{1}^{\sim}$  Bi  $_{2}^{\circ}$ . Example graphical results are shown in

Figs. 4 and 5 where the dimensionless resistance  $\psi$  is plotted against  $\alpha$  and  $\epsilon$  for the fixed Biot numbers Bi  $_1$  = Bi  $_2$  = .01 and Bi  $_2$  = Bi = .1.

A comparison of Figs. 4 and 5 shows that for similar geometry, an increase in the Biot number from .01 to .1 causes a substantial reduction in the thermal resistance of the board. However, changes in thermal resistance which result from different geometrical configurations are much more difficult to interpret from plots such as Figs. 4 and 5. For example, consider a case where  $\alpha$  = .05,  $\epsilon$  = .4 and Bi  $Bi_2 = .01$  (see Fig. 4). If the aspect ratio (or thickness of the board) is increased to  $\alpha = .5$ , then Fig. 4 seems to indicate an increase in the thermal resistance for Bi = .01. In comparing practical problems in microelectronics packaging, though, the increase in board thickness is usually intended for fixed values of the convective heat transfer coefficients and the thermal conductivity. Thus a factor of 10 increase in thickness not only raises  $\boldsymbol{\alpha}$  from .05 to .5 but also the Biot numbers from .01 to .1.

Fig. 4 Dimensionless Resistance Versus Board Aspect Ratio and Relative Contact Size for Bi<sub>1</sub>=Bi<sub>2</sub>=.01

Fig. 5 Dimensionless Resistance Versus Board Aspect Ratio and Relative Contact Size for Bi<sub>1</sub>=Bi<sub>2</sub>=.1

examination of Fig. 5 now shows a decrease in ermal resistance. Similar ambiguity results with hanges in  $\epsilon$ . For example, if one wishes to investigate the effect of halving the spacing between IC chips on the board then not only will  $\epsilon$  increase by a factor of 2 but also  $\alpha$  for a fixed board thickness. Therefore presentation of extensive results in the form of the four dimensionless parameters is not just unfeasible but also potentially confusing.

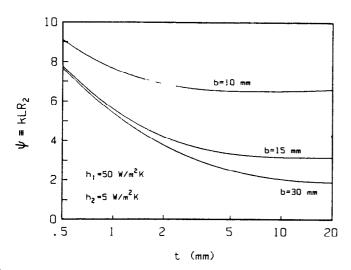

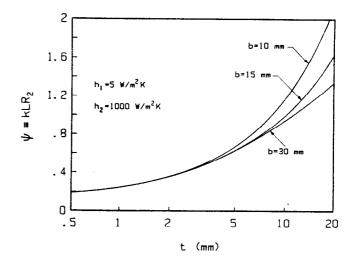

A specific example problem is now examined to better illustrate the impact of different convective cooling and geometrical configurations on the thermal performance of a microelectronic circuit board. this example problem an integrated circuit chip 15 mm in width is placed on a circuit board with thermal conductivity of 1 W/mK at center-to-center spacings of 20, 30, and 60 mm and heat transfer coefficients typical of both free and forced air cooling are prescribed. With reference to the basis problem illustrated in Fig. 3, the appropriate parameters are then

a = 7.5 mmk = 1 W/mKb = 10, 15, 30 mm $5 \le h_1 = h_2 \le 100 \text{ W/m}^2 \text{K}$ .5  $\leq$  t  $\leq$  20 mm

With the exception of the board thickness t, these values are believed to be indicative of potential situations encountered in surface-mount packaging of integrated circuit chips. The unrealistic range board thicknesses from the very thin (.5 mm) to the extremely thick (20 mm) is considered so that a complete range of thermal responses due to the chip spacing-board thickness interaction can be illustra-For integrated circuit chips of widths other than 15 mm and board conductivities different from k=1 W/mK, the "thin-board" or "thick-board" effects shown in this example problem may become important even for typical board thicknesses. On this note the reader is cautioned that extrapolations from the results to follow should be made very carefully. Implementation of the expressions for thermal resistance derived in this work is fairly straightforward and is encouraged so that approximate thermal optimization of microelectronic circuit boards can be accomplished on an individual case basis.

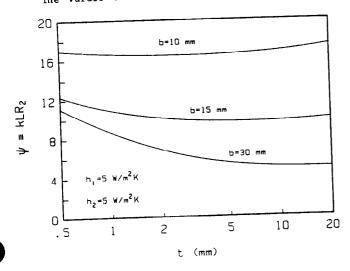

The values of the dimensionless thermal resis-

Fig. 6 Dimensionless Resistance of Example Problem for  $h_1 = h_2 = 5 \text{ W/m}^2 \text{K}$

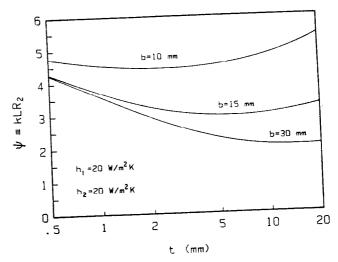

Dimensionless Resistance of Example Problem for  $h_1=h_2=20 \text{ W/m}^2\text{K}$

tance,  $\psi\equiv kLR_2$ , computed for this example problem are summarized graphically in Figs. 6-9. The results for convective coefficients typical of natural convection cooling are shown in Figs. 6 and 7. For  $h_1 =$ h<sub>2</sub> = 5 W/m<sup>2</sup>K, Fig. 6 shows clearly that major reductions in thermal resistance arise by increasing the chip spacing (i.e. larger b) but board thickness has little effect especially for small b(or large  $\varepsilon \Xi a/b$ ). When  $h_1 = h_2 = 20 \text{ W/m}^2\text{K}$  as shown in Fig. 7 though, the influence of board thickness is far more significant. In fact, in this situation substantial reductions in thermal resistance due to increased chip spacing are realized only when sufficiently thick boards are available to allow heat flow to the extended surface area with minimal constriction resistance. However, it is now possible to have a board which is too thick for a given chip spacing because a substantial fraction of the total heat flow exits via the bottom surface and an increased thickness also increases the solid resistance between the chip and

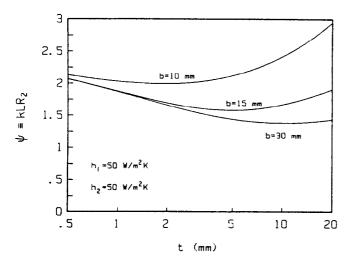

The results shown in Figs. 8 and 9 are more indicative of situations encountered in forced-air cooling of microelectronic circuit boards. Fig. 8 where  $h_1 = h_2 = 50$  W/m<sup>2</sup>K, the effect of increased chip spacing is seen to be minimal for  $b \ge 15$ mm and typical board thicknesses on the order of t = 2 mm. Furthermore, an "optimized" thickness for convective cooling with  $h_1 = h_2$  20 W/m<sup>2</sup>K and b = 30mm gives a thermal resistance nearly identical to that of  $h_1 = h_2 = 50 \text{ W/m}^2 \text{K}$  with b = 30 mm and t = 2When the convective heat transfer coefficients are increased to  $h_1 = h_2 = 100 \text{ W/m}^2 \text{K}$  as shown in Fig. 9, chip spacing has almost no effect except for very thick boards and the thinner boards are generally seen to be less resistive.

A special case which may occasionally occur, for example, due to an enclosure of the bottom surface of a microelectronic circuit board, is considered in Fig. 10. In this problem h<sub>1</sub> = 50 W/m<sup>2</sup>K provides a much higher heat transfer coefficient to the top surface than that of the bottom where  $h_2 = 5 \text{ W/m}^2 \text{K}$ . In this case board thicknesses below some given value at each chip spacing tend to "choke-off" the heat flow

Fig. 8 Dimensionless Resistance of Example Problem for  $h_1 = h_2 = 50$  W/m<sup>2</sup>K

Fig. 9 Dimensionless Resistance of Example Problem for  $h_1 = h_2 = 100 \text{ W/m}^2 \text{K}$

Fig. 10 Dimensionless Resistance of Example Problem for  $h_1=50 \text{ W/m}^2\text{K}$  and  $h_2=5 \text{ W/m}^2\text{K}$

from the chip to the top surface of the board and thus increase the thermal resistance. Finally, Fig. Il summarizes another special case in which the addition of a high thermal conductivity, water-cooled cold plate attached to the bottom surface of the board with negligible contact resistance is simulated. For this situation it is desirable to keep the board as thin as possible and chip spacing has almost no effect. This allows dense packaging of integrated circuit chips to be used with little thermal penalty.

The relative importance of convective cooling by the heat flow path through the bottom surface of the integrated circuit chip can be illustrated by considering the effective heat transfer coefficients on the top and bottom surfaces of the chip, or hel and help respectively. The heat transfer coefficient on the top surface of the chip can be approximated as being the same as that on the top surface of the circuit board, or

$$h_{el} \approx h_{l} \tag{33}$$

The bottom coefficient  $h_{e2}$  can be found by interpreting the thermal resistance  $R_2$  as an effective heat transfer coefficient on the bottom surface of the integrated circuit chip, or

$$h_{e2} \approx \frac{k}{\mu_a} \tag{34}$$

By using values of  $\psi$  computed for the example problem where a = 7.5 mm and k = 1 W/m K, comparitive values of  $h_{e1}$  and  $h_{e2}$  have been compiled in Table i for a variety of convective coefficients  $h_1$  and  $h_2$  and chip spacings b. Note that a board thickness of t = 2 mm is assumed for all results shown in Table 1. Note further that the values of  $h_{e1}$  reported in Table 1 are probably too low relative to  $h_1$  and  $h_2$  as the work of Culham (1985) shows that heat transfer coefficients on a chip are usually around 50% higher than that of the top surface of the circuit board. In addition the values of  $h_{e2}$  reported in Table 1 are probably too high relative to  $h_1$  and  $h_2$  due to the neglect of contact resistance between the integrated circuit chip and the circuit board. Nonetheless, the

Fig. 11 Dimensionless Resistance of Example Problem for  $h_1$ =5 W/m<sup>2</sup>K and  $h_2$ =1000 W/m<sup>2</sup>K

| h <sub>1</sub>       | h <sub>2</sub>       | b    | h <sub>el</sub>      | h <sub>e2</sub>      |

|----------------------|----------------------|------|----------------------|----------------------|

| (W/m <sup>2</sup> K) | (W/m <sup>2</sup> K) | (mm) | (W/m <sup>2</sup> K) | (W/m <sup>2</sup> K) |

|                      |                      | 10   |                      | 8.1                  |

| 5                    | 5                    | 15   | 5                    | 13.3                 |

|                      |                      | 30   |                      | 19.6                 |

|                      |                      | 10   |                      | 30.2                 |

| 20                   | 20                   | 15   | 20                   | 41.4                 |

|                      |                      | 30   |                      | 45.8                 |

|                      |                      | 10   |                      | 67.0                 |

| 50                   | 50                   | 15   | 50                   | 78.9                 |

|                      |                      | 30   | 1                    | 80.7                 |

|                      |                      | 10   |                      | 115                  |

| 100                  | 100                  | 15   | 100                  | 124                  |

|                      |                      | 30   | 1                    | 125                  |

|                      |                      | 10   |                      | 19.4                 |

| 50                   | 5                    | 15   | 50                   | 31.2                 |

|                      |                      | 30   | 1                    | 35.3                 |

|                      | <b>†</b>             | 10   |                      | 371                  |

| 5                    | 1000                 | 15   | 5                    | 373                  |

|                      |                      | 30   |                      | 373                  |

Table 1. Effective heat transfer coefficients for an integrated circuit chip with a = 7.5 mm, k = 1 W/mK, and t = 2 mm.

results in Table 1 still indicate clearly that a significant portion of the total heat flow from an integrated circuit chip can exit via the bottom heat flow path  $\mathbb{Q}_2$  in Fig. 2 for practical applications with surface-mount packaging. Thus analysis and optimization of the heat flow path into the circuit board is seen to be an important step towards a final goal of allowing maximum power density for a given maximum device operating temperature with minimum cost.

# A ONE-DIMENSIONAL MODEL: THE COMPOUND-FIN

As mentioned previously, an accurate prediction of the thermal performance of microelectronic circuit boards really requires consideration of the interaction between the thermal-fluid boundary layer and heat conduction in the circuit board. To achieve this goal with a minimum of computational effort, Culham (1985) has coupled a boundary layer analysis with a one-dimensional heat conduction model, the compound-fin. In this approximate heat conduction model the temperature is assumed to vary only along the length of the board, or T=T(x) only in Fig. 3. Physically, this approximation indicates that temperature changes in the x-direction of Fig. 3 are much greater than those in the z-direction or that the temperature drop in the z-direction of the solid is much less than the temperature drop across the thermal boundary layer.

In a compound-fin approximation, the prescribed heat flux and convective cooling on the top and bottom surfaces of the fundamental basis problem shown in Fig. 3 are modelled as sources and sinks respectively in a one-dimensional heat balance equation. By solving the simple constant-coefficient ordinary differential equation which results and applying the boundary conditions of adiabatic ends at x=0 and x=b, the dimensionless thermal resistance of the compound-fin approximation of Fig. 3 can easily be derived as

$$\psi_{CF} = \frac{\alpha}{\varepsilon} \left\{ \frac{1}{Bi_2} + \frac{c_1}{m_1 \varepsilon} \left( e^{m_1 \varepsilon} - e^{-m_1 \varepsilon} \right) \right\}$$

(35)

where  $m_1 \equiv \sqrt{Bi_2} / \alpha$  (36)

$$m_2 \equiv \sqrt{Bi_1 + Bi_2} / \alpha \tag{37}$$

and

$$C_1 = \frac{1/Bi_2}{\frac{m_1\sigma_1}{m_2} (e^{m_2(\varepsilon-2)} + e^{-m_2\varepsilon}) - e^{-m_1\varepsilon} - e^{m_1\varepsilon}}$$

(38)

$$\sigma_{1} = \frac{e^{m_{1}\varepsilon} - e^{-m_{1}\varepsilon}}{e^{m_{2}(\varepsilon-2)} - e^{-m_{2}\varepsilon}}$$

(39)

These expressions are not valid when the bottom surface is insulated, or Bi  $_2^{\sim}$  0. In this case a similar one-dimensional analysis can show that

$$\psi_{CF}(Bi_2=0) = C_2 \frac{\alpha}{\varepsilon} - \frac{\varepsilon}{6\alpha}$$

(40)

where

$$c_2 = c_3(e^{-m_2\epsilon} + e^{m_2(\epsilon-2)}) + \epsilon^2/2\alpha^2$$

(41)

$$c_3 = \varepsilon/m_2\alpha^2(e^{-m_2\varepsilon} - e^{m_2(\varepsilon-2)})$$

(42)

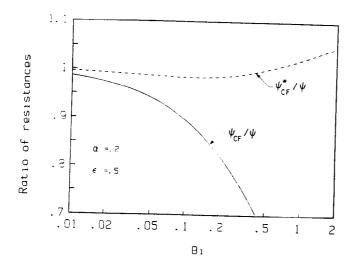

In Fig. 12 the ratio of the compound-fin resistance to the exact two-dimen-sional resistance,  $\psi_{\rm CF}/\psi$ , is plotted against Bi=Bi $_1$ =Bi $_2$  for the case of  $\varepsilon$ =.5 and  $\alpha$ =.2. Examination of extensive numerical results has shown that errors in  $\psi_{\rm CF}$  relative to  $\psi$  of Eq. (31) generally decrease as  $\varepsilon$  increases and  $\alpha$  decreases. Furthermore when Bi $_1$  the error in  $\psi_{\rm CF}$  is usually less than that shown in Fig. 12 for Bi=max (Bi $_1$ ,Bi $_2$ ).

From Fig. 12 the compound-fin model is found to underpredict the true thermal resistance. This is expected since its derivation assumes that internal solid resistances are small relative to film resistances and thus neglects their contribution. The relative error in  $\psi_{\rm CF}$  for the case shown in Fig. 12 is generally on the order of the Biot number for Bi  $\leq$  .5. Therefore, if errors in resistance greater than 10% are not tolerable, then the one-dimensional approximation given by the compound-fin model is of limited utility for Bi  $\geq$  .1. In fact, the actual surface temperatures (which are required in a model that couples heat conduction and boundary-layer analyses) may be significantly more in error for a given Biot number than the resistance which is based on an average temperature.

Physically the Biot number should reflect the

Fig. 12 Ratio of 1-D to 2-D Resistances for the Compound-Fin Model ( $\psi_{CF}^{+}/\psi$ ) and the Modified Compound-Fin Model ( $\psi_{CF}^{+}/\psi$ ) Versus Biot Number B<sub>1</sub> for top and bottom surfaces

ratio of the solid resistance,  $R_g$ , to the fluid-film resistance,  $R_f$ , in a system or  $\operatorname{Bi} \approx R / R_f$ . For "small" Biot numbers one might approximate the total thermal resistance,  $R_f$ , as the sum of the solid and fluid-film resistances acting in series, or

$$R_t \approx R_s + R_f \approx R_f(1 + Bi)$$

which suggests that a better estimation of the thermal resistance of the basis problem of Fig. 3 can be made using a compound-fin model if the factor (1+Bi) is applied to  $\psi_{\rm CF}$  to give

$$\psi_{CF}^{\star} = \psi_{CF}^{(1+Bi)} \tag{43}$$

A plot of  $\psi_{\mathbf{CF}}^{\star}/\psi$  is also shown in Fig. 12 and the increase in accuracy of this "modified" compound-fin model is substantial. Thus an important future improvement to the compound-fin model would be the development of similar correction factors which can better estimate actual surface temperatures while still using only a one-dimensional heat conduction model.

#### CONCLUSIONS

In this work an approximate model to predict the thermal resistance of convectively-cooled microelectronic circuit boards has been developed by considering a fundamental basis problem for heat conduction in the board. An approximate analytical solution to this basis problem which can provide any desired accuracy was derived by employing a novel approach for treating mixed boundary conditions. An individual problem of this type could be readily solved using standard numerical methods. However this approximate solution allows interactive evaluations of the thermal advantages or disadvantages for different circuit board configurations or convective cooling arrangements to be made rapidly on a personal computer.

The results obtained for a practical example problem indicate that either a "thin" or "thick" circuit board can be desirable depending on the interac-

tion of the different variables which contribute to the thermal resistance. In particular, a decrease in the thermal resistance of the board due to increased chip spacing often occurs only when accompanied by a similar increase in the board thickness (which is often not feasible). Thus increasing the chip center-to-center spacing to a distance greater than twice the chip width normally produces little benefit in decreased thermal resistance for the penalty of decreased packaging density except when the convective coefficients are fairly low (i.e. free convec-In some cases where the convective heat transfer coefficients are very high, it is desirable to make the board as thin as possible and the integrated circuit chips can be placed close together without increasing the thermal resistance of the circuit board.

Finally, the accuracy of the compound-fin model for one-dimensional steady heat conduction in a microelectronic circuit board has also been investigated. The compound-fin model underpredicts the actual thermal resistance with a relative error generally exceeding 10% for Bi > .1 where Bi is the maximum of the top and bottom surface Biot numbers. A substantial increase in the accuracy of the compound-fin model was observed when a simple correction factor derived from physical considerations was applied.

#### REFERENCES

Culham, J.R., 1985, "Calculation of Wall Temperature on a Flat Plate with Convection Cooling on the Front and Back Surfaces", University of Waterloo Microelectronics Heat Transfer Laboratory Report UW/MHTL 8506 G-09.

Negus, K.J., 1985, "Temperature Distributions in Contacting Electrical Conductors", University of Waterloo Microelectronics Heat Transfer Laboratory Report UW/MHTL 8505 G-07.

Negus, K.J., and Yovanovich, M.M., 1984, "Application of the Method of Optimized Images to Steady, Three-Dimensional Heat Conduction", ASME Paper No. 84-WA/HT-110, ASME Winter Annual Meeting, New Orleans, LA, Dec. 9-13.

Negus, K.J., and Yovanovich, M.M., 1985, "Thermal Constriction Resistance of Circular Contacts on Coated Surfaces: Effect of Contact Boundary Conditions", AIAA Paper No. 85-1014, AIAA 20th Thermophysics Conference, Williamsburg, VA, June 19-21.

PYovanovich, M.M., 1976, "General Expressions for Circular Constriction Resistances for Arbitrary Flux Distribution", Progress in Astronautics and Aeronautics: Radiative Transfer and Thermal Control, Vol. 49, ed. A.M. Smith, AIAA, New York, pp. 381-396.

# ACKNOWLEDGEMENTS

The authors acknowledge the financial support of this work provided by the Natural Sciences and Engineering Research Council of Canada under PRAI grant P8322 for Dr. Yovanovich and with a Postgraduate Scholarship for Mr. Negus.

APPENDIX I

The solution of Eq. (24) for the series coefficients  $A_n$  requires the evaluation of the matrix coefficients C and G. The coefficients C are determined by exact integration of Eq. (25) to accompany the solution of

$$\begin{split} \mathbf{C}_{\mathbf{m}n} &= \Delta_{\mathbf{m}n} \ \gamma_{3}^{2} (1 - \delta_{\mathbf{m}n}) \left[ n \pi \alpha \Omega_{\mathbf{n}} + m \pi \alpha \Omega_{\mathbf{m}} + B \mathbf{i}_{1} \right] \\ &+ \delta_{\mathbf{m}n} \left[ (n \pi \Omega_{\mathbf{n}} \alpha \gamma_{3})^{2} / 2 + \tau_{\mathbf{n}} \gamma_{3} (2 \gamma_{3} \pi \alpha \Omega_{\mathbf{n}} + B \mathbf{i}_{1}) \right] \\ &+ \Lambda_{\mathbf{n}} \Lambda_{\mathbf{m}} \left[ 2 \gamma_{4} B \mathbf{i}_{1} (1 - \epsilon) + \gamma_{4}^{2} + B \mathbf{i}_{1}^{2} (1 - \epsilon) - n \pi \Omega_{\mathbf{n}} \alpha \gamma_{3} \right. \\ &- m \pi \Omega_{\mathbf{m}} \alpha \gamma_{3} - 2 \gamma_{3} (\gamma_{4} + B \mathbf{i}_{1}) \right] \end{split} \tag{A-1}$$

where  $\delta_{mn}$  is the familiar Kronecker delta function,  $_{n}^{n}$  ,  $_{n}^{mn}$  , and  $_{3}^{n}$  are defined by Eqs. (11), (13) and (14) respectively, and

$$\Delta_{mn} = (-Bi_1/2)\left[\frac{\sin(n-m)\pi\varepsilon}{(n-m)\pi} + \frac{\sin(n+m)\pi\varepsilon}{(n+m)\pi}\right] \quad (A-2)$$

$$\tau_n = Bi_1[(1-\epsilon)/2 - \frac{\sin 2n\pi\epsilon}{4n\pi}]$$

(A-3)

$$\gamma_4 = Bi_2/Bi_2 + 1$$

(A-4)

The coefficients  $G_n$  are determined similarly by exact integration of Eq. (26) to give  $G_n = \frac{2}{3} \frac{\Omega}{n} \alpha \sin n\pi\epsilon +$

$$G_n = \gamma_3^2 \Omega_n \alpha \sin n\pi\epsilon +$$

$$\epsilon \Lambda_n [Bi_3^2(1-\epsilon) - \gamma_4^2 - \gamma_3 (Bi_1 + n\pi\Omega_n \alpha)]$$

(A-5)